## ZDSD01G/02G/04G/08G/16G/32G SD NAND Datasheet

\* Information furnished is believed to be accurate and reliable. However, Zetta assumes no responsibility for the consequences of use of such information or for any infringement of patents of other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent rights of Zetta. Specifications mentioned in this publication are subject to change without notice. This publication supersedes and replaces all information previously supplied. Zetta products are not authorized for use as critical components in life support devices or systems without express written approval of Zetta. The Zetta logo is a registered trademark of Zetta Device Technology Limited. All other names are the property of their respective own.

### 1. Introduction

Zetta SD NAND is an embedded storage solution designed in a LGA8 package form. The operation of SD NAND is similar to an SD card which is an industry standard.

SD NAND consists of NAND flash and a high-performance controller. 3.3V supply voltage is required for the NAND area (VCC). SD NAND is fully compliant with SD2.0 interface, which is utilized by most of general CPU. The advantages of the SD NAND include high quality, low power consumption and cost performance.

### 2. Product List

| Capacity   | Part number  | Package                | Size    |

|------------|--------------|------------------------|---------|

| 1Gb (SLC)  | ZDSD01GLGEAG | LGA8 (Land Grid Array) | 8x6mm   |

| 2Gb (SLC)  | ZDSD02GLGEAG | LGA8 (Land Grid Array) | 8x6mm   |

| 4Gb (SLC)  | ZDSD04GLGEAG | LGA8 (Land Grid Array) | 8x6mm   |

| 8Gb (MLC)  | ZDSD08GLGEAG | LGA8 (Land Grid Array) | 8x6.2mm |

| 16Gb (MLC) | ZDSD16GLGEGA | LGA8 (Land Grid Array) | 8x6.2mm |

| 32Gb (MLC) | ZDSD32GLGEGA | LGA8 (Land Grid Array) | 8x6.2mm |

| 1Gb (SLC)  | ZDSD01GLGIAG | LGA8 (Land Grid Array) | 8x6mm   |

| 2Gb (SLC)  | ZDSD02GLGIAG | LGA8 (Land Grid Array) | 8x6mm   |

| 4Gb (SLC)  | ZDSD04GLGIAG | LGA8 (Land Grid Array) | 8x6mm   |

| 8Gb (MLC)  | ZDSD08GLGIAG | LGA8 (Land Grid Array) | 8x6.2mm |

| 16Gb (MLC) | ZDSD16GLGIGA | LGA8 (Land Grid Array) | 8x6.2mm |

| 32Gb (MLC) | ZDSD32GLGIGA | LGA8 (Land Grid Array) | 8x6.2mm |

Note: R/W Cycle: SLC(100,000), MLC(6,000)

### 3. Features

- ✓ Support up to 50Mhz clock frequency

- √ Support 1/4 bit mode

- ✓ Built-in HW ECC Engine and highly reliable NAND management mechanism

- High Speed model, Speed class 4/class 6/class 8/class10 supported.

- √ Smaller package LGA8 (Land Grid Array)

- ✓ Operation Conditions Temperature Range: Extended Ta = -25  $^{\circ}$ C to +85  $^{\circ}$ C

Industrial Ta =  $-40^{\circ}$ C to  $+85^{\circ}$ C

✓ Storage Conditions Temperature Range: Tstg = -65  $^{\circ}$ C to +150  $^{\circ}$ C

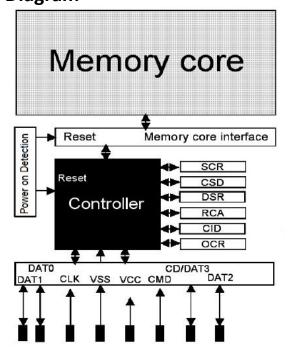

## 4. Block Diagram

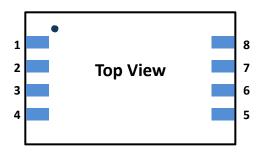

# 5. Pin Assignments

| Pin No. | Pin name (SD mode)  | Pin name (SPI mode) |

|---------|---------------------|---------------------|

| 1       | SD2, I/O pin        | NC, no connection   |

| 2       | SD3, I/O pin        | /CS, chip select    |

| 3       | CLK, clock signal   | CLK, clock signal   |

| 4       | Vss, ground         | Vss, groud          |

| 5       | CMD, command signal | DI, data in         |

| 6       | SD0, I/O pin        | DO, data out        |

| 7       | SD1, I/O pin        | NC, no connection   |

| 8       | Vdd, power supply   | Vdd, power supply   |

# 6. Usage

#### **6.1. Product Protocol**

As SD NAND is the realize SD2.0 standard product, thus please refer to the SD2.0 related protocol: SD Physical Layer Specification Version 2.00.

### 6.2. DC Characteristics

| Item                     |            | Symbol | MIN       | MAX       | Unit | Note                              |

|--------------------------|------------|--------|-----------|-----------|------|-----------------------------------|

| Supply voltage           |            | VDD    | 2.7       | 3.6       | V    |                                   |

| Input voltage            | High Level | VIH    | VDD*0.625 | VDD+0.3   | V    |                                   |

| Input voltage            | Low Level  | VIL    | Vss-0.3   | VDD*0.25  | V    |                                   |

| Outrout valtage          | High Level | Voн    | VDD*0.75  |           | V    | IOH=-2mA,<br>VDD=VDDmin           |

| Output voltage           | Low Level  | VCL    |           | VDD*0.125 | ٧    | IOL=2ma,<br>VDD=VDDmin            |

| Standby Current(*)       |            | land   |           | 20*       | A    | VDD=3.6V,<br>clock 25MHz          |

|                          |            | lcc1   |           | 0.2       | mA   | VDD=3.0V, clock<br>STOP, Ta=25° C |

| Writ                     |            | ı      |           | 25        | Л    | 2 ()//258411- 508411-             |

| Operation Current(       | Read       | I      |           | 25        | mA   | 3.6V/25MHz,50MHz                  |

| Input voltage setup Time |            | Vrs    |           | 250       | ms   |                                   |

Note: Standby current max 20mA with CLOCK 25Mhz only based on 100 pcs samples

**Peak Voltage and Leak Current**

| Tour Touring and Louis Controll        |        |      |         |      |      |  |  |

|----------------------------------------|--------|------|---------|------|------|--|--|

| Item                                   | Symbol | MIN  | MAX     | Unit | Note |  |  |

| Peak voltage on all lines              |        | -0.3 | VDD+0.3 | ٧    |      |  |  |

| Input Leakage Current for all pins     |        | -10  | 10      | uA   |      |  |  |

| Output Leakage Current for all outputs |        | -10  | 10      | uA   |      |  |  |

**Signal Capacitance**

| Pull up Resistance                         | RCMD/RDAT | 10 | 100 | k  |                           |

|--------------------------------------------|-----------|----|-----|----|---------------------------|

| Total bus capacitance for each signal line | CL        | -  | 40  | pF | 1 card<br>Сноsт+Свus≤30pF |

| Card Capacitance for signal pin            | Ccard     | -  | 10  | pF |                           |

| Pull up Resistance inside card (pin1)      | RDAT3     | 10 | 90  | k  |                           |

| Capacity Connected to Power line           | Cc        | -  | 5   | pF |                           |

Note: WP pull-up (Rwp) Value is depend on the Host Interface drive circuit.

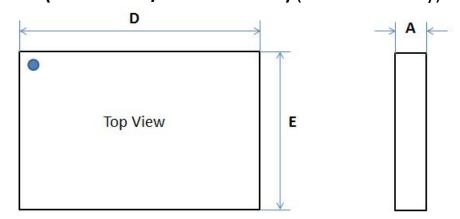

# 7. Package Dimensions

# LGA8 (SLC 8x6mm/MLC 8x6.2mm) (Land Grid Array)

### Dimensions:

| Symbol<br>Unit |      | Α    | b    | D    | E-SLC | E MI C | е    | L    |

|----------------|------|------|------|------|-------|--------|------|------|

|                |      | А    | b    |      | E-3LC | E-MLC  |      |      |

|                | Min  | 0.75 | 0.55 | 7.95 | 5.90  | 6.10   |      | 0.75 |

| Mm             | Norm | 0.80 | 0.60 | 8.00 | 6.00  | 6.20   | 1.27 | 0.80 |

|                | Max  | 0.85 | 0.65 | 8.05 | 6.10  | 6.30   |      | 0.85 |

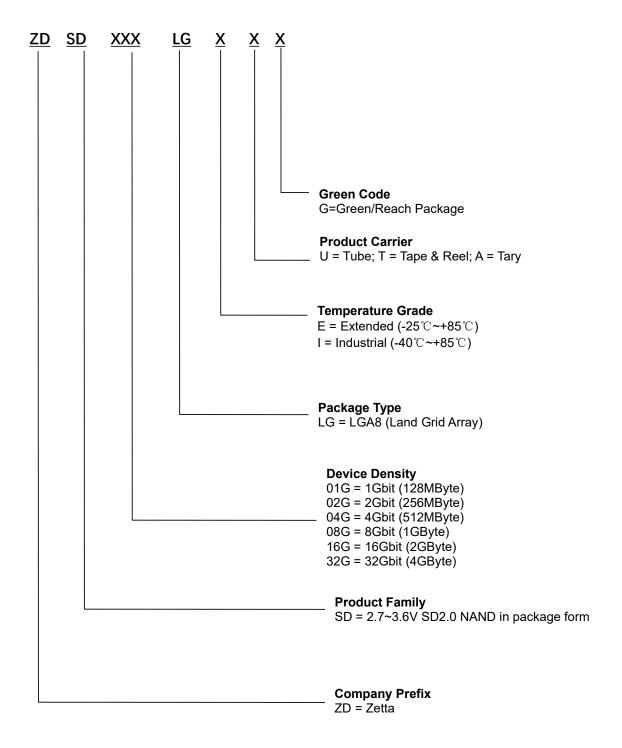

## 8. Ordering Information

The ordering part number is formed by a valid combination of the following

# 9. Revision History

| Version No. | Change Description                                                       | Date       |

|-------------|--------------------------------------------------------------------------|------------|

| V1.0        | Initial release, part number is based on extended temperature, LGA 8*6mm | 2020/06/02 |

| V1.1        | Add 32Gb MLC SD Nand                                                     | 2021/12/01 |

| V1.2        | Ordering Information Update                                              | 2022/2/20  |