Zetta

### **Zetta 4Gbit DDR4 SDRAM**

#### **Datasheet**

#### **Features**

- VDD=VDDQ=1.2V +/- 0.06V

- Fully differential clock inputs (CK, CK ) operation

- Differential Data Strobe (DQS, DQS )

- On chip DLL align DQ, DQS and DQS transition with CK transition

- DM masks write data-in at the both rising and falling edges of the data strobe

- All addresses and control inputs except data, data strobes and data masks latched on the rising edges of the clock

- Programmable CAS latency 9, 11, 12, 13, 14, 15 and 16, 17, 18 supported

- Programmable additive latency 0, CL-1, and CL-2 supported

- Programmable CAS Write latency (CWL) = 9, 10, 11, 12, 14, 16

- Programmable burst length 4/8 with both nibble sequential and interleave mode

- · BL switch on the fly

- 16banks

- Average Refresh Cycle (Tcase of 0 oC~ 95 oC)

- 7.8 μs at 0oC ~ 85 oC

- 3.9 µs at 85oC ~ 95 oC•

- JEDEC standard 78ball FBGA

- · Driver strength selected by MRS

- Dynamic On Die Termination supported

- · Self Refresh Abort is supported

- DBI(Data Bus Inversion) is supported(x8)

- Two Termination States such as RTT\_PARK and RTT\_NOM switchable by ODT pin

- · Asynchronous RESET pin supported

- · ZQ calibration supported

- TDQS (Termination Data Strobe) supported

- · Write Levelization supported

- 8 bit pre-fetch

- This product in compliance with the RoHS directive.

- Internal Vref DQ level generation is available

- · Write CRC is supported at all speed grades

- Maximum Power Saving Mode is supported

- TCAR(Temperature Controlled Auto Refresh) mode is supported

- LP ASR(Low Power Auto Self Refresh) mode is sup-ported

- Fine Granularity Refresh is supported

- Per DRAM Addressability is supported

- Geardown Mode(1/2 rate, 1/4 rate) is supported

- Programable Preamble for read and write is supported

- CA parity (Command/Address Parity) mode is sup-ported

- Bank Grouping is applied, and CAS to CAS latency (tCCD\_L, tCCD\_S) for the banks in the same or different bank group accesses are available

### 1. Description

The DDR4 SDRAM is a 4Gb CMOS Double Data Rate IV (DDR4) Synchronous DRAM, ideally suited for the main memory applications which requires large mem-ory density and high bandwidth. Zetta 4Gb DDR4 SDRAMs offer fully synchronous operations refer-enced to both rising and falling edges of the clock. While all addresses and control inputs are latched on the rising edges of the CK (falling edges of the CK), Data, Data strobes and Write data masks inputs are sampled on both rising and falling edges of it. The data paths are internally pipelined and 8-bit prefetched to achieve very high bandwidth.

### 2. Package Ballout/Mechanical Dimension

x8 Package Ball out (Top view): 78ball FBGA Package

|   | 1       | 2           | 3         | 4 | 5 | 6 | 7                    | 8            | 9       |   |   |

|---|---------|-------------|-----------|---|---|---|----------------------|--------------|---------|---|---|

| Α | VDD     | VSSQ        | TDQS_c    |   |   |   | DM_n/DBI_n<br>TDQS_t | vssq         | vss     |   | Α |

| В | VPP     | VDDQ        | DQS_c     |   |   |   | DQ1                  | VDDQ         | ZQ      |   | В |

| С | VDDQ    | DQ0         | DQS_t     |   |   |   | VDD                  | vss          | VDDQ    |   | С |

| D | VSSQ    | DQ4         | DQ2       |   |   |   | DQ3                  | DQ5          | VSSQ    |   | D |

| E | vss     | VDDQ        | DQ6       |   |   |   | DQ7                  | VDDQ         | vss     |   | Е |

| F | VDD     | NC          | ODT       |   |   |   | CK_t                 | CK_c         | VDD     |   | F |

| G | vss     | NC          | CKE       |   |   |   | CS_n                 | NC           | TEN     |   | G |

| н | VDD     | WE_n<br>A14 | ACT_n     |   |   |   | CAS_n<br>A15         | RAS_n<br>A16 | vss     |   | н |

| J | VREFCA  | BG0         | A10<br>AP |   |   |   | A12<br>BC_n          | BG1          | VDD     |   | J |

| K | VSS     | BA0         | A4        |   |   |   | А3                   | BA1          | vss     |   | K |

| L | RESET_n | A6          | A0        |   |   |   | A1                   | A5           | ALERT_n |   | L |

| M | VDD     | A8          | A2        |   |   |   | A9                   | A7           | VPP     |   | M |

| N | vss     | A11         | PAR       |   |   |   | NC                   | A13          | VDD     |   | N |

|   |         |             |           |   |   |   |                      |              |         | _ |   |

|   | 1       | 2           | 3         | 4 | 5 | 6 | 7                    | 8            | 9       |   |   |

(Top View: See the balls through the Package)

- Populated ball

- + Ball not populated

# 3. Pin Functional Descriptions

| Symbol                               | Туре  | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|--------------------------------------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CK_t, CK_c                           | Input | Clock: CK_t and CK_c are differential clock inputs. All address and control input signals are sampled on the crossing of the positive edge of CK_t and negative edge of CK_c.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| CKE,<br>(CKE1)                       | Input | Clock Enable: CKE HIGH activates, and CKE Low deactivates, internal clock signals and device input buffers and output drivers. Taking CKE Low provides Precharge Power-Down and Self-Refresh operation (all banks idle), or Active Power-Down (row Active inany bank). CKE is asynchronous for Self-Refresh exit. After VREFCA and VREFDQ have become stable during the power on and initialization sequence, they must be maintained during all operations (including Self-Refresh). CKE must be maintained high throughout read and write accesses. Input buffers, excluding CK, CK_c, ODT and CKE, are disabled during power-down. Input buffers, excluding CKE, are disabled during Self-Refresh. |

| CS_n,<br>(CS1_n)                     | Input | Chip Select: All commands are masked when CS_n is registered HIGH. CS_n provides for external Rank selection on systems with multiple Ranks. CS_n is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| C0,C1,C2                             | Input | Chip ID: Chip ID is only used for 3DS for 2,4,8high stack via TSV to select each slice of stacked compnent. Chip ID is considered part of the command code.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| ODT,<br>(ODT1)                       | Input | On Die Termination: ODT (registered HIGH) enables termination resistance internal to the DDR4 SDRAM. When enabled, ODT is only applied to each DQ, DQS_t, DQS_c and DM_n/DBI_n/TDQS_t,NU/TDQS_c (When TDQS is enabled via Mode Register A11=1 in MR1) signal for x8 configurations. The ODT pin will be ignored if MR1 is programmed to disable RTT_NOM.                                                                                                                                                                                                                                                                                                                                              |

| ACT_n                                | Input | Activation Command Input: ACT_n defines the Activation command being entered along with CS_n. The input into RAS_n/A16, CAS_n/A15 and WE_n/A14 will be considered as Row Address A16, A15 and A14.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RAS_n/A16,<br>CAS_n/A15,<br>WE_n/A14 | Input | Command Inputs RAS_n/A16, CAS_n/A15 and WE_n/A14 (along with CS_n) define the command being entered. Those pins have multi function. For example, for activation with ACT_n Low, those are Addressing like A16,A15 and A14 but for non-activation command with ACT_n High, those are Command pins for Read, Write and other command defined in command truth table.                                                                                                                                                                                                                                                                                                                                   |

| Symbol                                                                  | Type             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DM_n/DBI_<br>n/<br>TDQS_t,<br>(DMU_n/DB<br>IU_n),<br>(DML_n/DB<br>IL_n) | Input/<br>Output | Input Data Mask and Data Bus Inversion: DM_n is an input mask signal for write data. Input data is masked when DM_n is sampled LOW coincident with that input data during a Write access. DM_n is sampled on both edges of DQS. DM is muxed with DBI function by Mode Register A10,A11,A12 setting in MR5. For x8 device, the function of DM or TDQS is enabled by Mode Register A11 setting in MR1. DBI_n is an input/output identifing wherther to store/output the true or inverted data. If DBI_n is LOW, the data will bestored/output after inversion inside the DDR4 SDRAM and not inverted if DBI_n is HIGH. TDQS is only supported in x8. |

| BG0 - BG1                                                               | Input            | Bank Group Inputs: BG0 - BG1 define to which bank group an Active, Read, Write or Precharge command is being applied. BG0 also determines which mode register is to be accessed during a MRS cycle. x8 have BG0 and BG1.                                                                                                                                                                                                                                                                                                                                                                                                                           |

| BA0 - BA1                                                               | Input            | Bank Address Inputs: BA0 - BA1 define to which bank an Active, Read, Write or Precharge command is being applied. Bank address also determines if the mode register or extended mode register is to be accessed during a MRS cycle.                                                                                                                                                                                                                                                                                                                                                                                                                |

| A0 - A17                                                                | Input            | Address Inputs: Provied the row address for ACTIVATE Commands and the column address for Read/Write commands th select one location out of the memory array in the respective bank. (A10/AP, A12/BC_n, RAS_n/A16, CAS_n/A15 and WE_n/A14 have additional functions, see other rows. The address inputs also provide the op-code during Mode Register Set commands.                                                                                                                                                                                                                                                                                 |

| A10 / AP                                                                | Input            | Auto-precharge: A10 is sampled during Read/Write commands to determine whether Autoprecharge should be performed to the accessed bank after the Read/Write operation.(HIGH: Autoprecharge; LOW: no Autoprecharge).A10 is sampled during a Precharge command to determine whether the Precharge applies to one bank (A10 LOW) or all banks (A10 HIGH). If only one bank is to be precharged, the bank is selected by bank addresses.                                                                                                                                                                                                                |

| A12 / BC_n                                                              | Input            | Burst Chop: A12 / BC_n is sampled during Read and Write commands to determine if burst chop (on-the-fly) will be performed. (HIGH, no burst chop; LOW: burst chopped). See command truth table for details.                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RESET_n                                                                 | Input            | Active Low Asynchronous Reset: Reset is active whenRESET_n is LOW, and inactive when RESET_n is HIGH. RESET_n must be HIGH during normal operation. RESET_n is a CMOS rail to rail signal with DC high and low at 80% and 20% of VDD.                                                                                                                                                                                                                                                                                                                                                                                                              |

| Symbol                                       | Type              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------------------------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DQ                                           | Input /<br>Output | Data Input/ Output: Bi-directional data bus. If CRC is enabled via Mode register then CRC code is added at the end of Data Burst. Any DQ from DQ0~DQ3 may indicate the internal Vref level during test via Mode Register Setting MR4 A4=High. During this mode, RTT value should be set to Hi-Z. Refer to vendor specific datasheets to determine which DQ is used.                                                                                                                                                                                                         |

| DQS_t, DQS_c, DQSU_t, DQSU_c, DQSL_t, DQSL_c | Input /<br>Output | Data Strobe: output with read data, input with write data. Edge-aligned with read data, centered in write data. For x16, DQSL corresponds to the data on DQL0-DQL7; DQSU corresponds to the data on DQU0-DQU7. The data strobe DQS_t, DQSL_t, and DQSU_t are paired with differential signals DQS_c, DQSL_c, and DQSU_c, respectively, to provide differential pair signaling to the system during reads and writes. DDR4 SDRAM supports differential data strobe only and does not support single-ended.                                                                   |

| TDQS_t,<br>TDQS_c                            | Output            | Termination Data Strobe: TDQS_t/TDQS_c is applicable for x8 DRAMs only. When enabled via Mode Register A11 = 1 in MR1, the DRAM will enable the same termination resistance function on TDQS_t/TDQS_c that is applied to DQS_t/DQS_c. When disabledvia mode register A11 = 0 in MR1, DM/DBI/TDQS will provide the data mask function or Data Bus Inversion depending on MR5; A11, 12, 10 and TDQS_c is not used.                                                                                                                                                            |

| PAR                                          | Input             | Command and Address Parity Input: DDR4 Supports Even Parity check in DRAMswith MR setting. Once it's enabled via Register in MR5, then DRAM calculates Parity with ACT_n, RAS_n/A16, CAS_n/A15, WE_n/A14, BG0-BG1, BA0-BA1, A17-A, and C0-C2(3DS devices). Input parity should maintain at the rising edge of the clock and at the same time with command & address with CS_n LOW.                                                                                                                                                                                          |

| ALERT_n                                      | Output            | Alert: It has multi functions such as CRC error flag, Command and Address Parity error flag as Output signal. If there is error in CRC, then Alert_n goes LOW for the period time interval and goes back HIGH. If there is error in Command Address Parity Check, then Alert_n goes LOW for relatively long period until on going DRAM internal recovery transaction to complete. During Connectivity Test mode, this pin works as input. Using this signal or not is dependent on system. In case of not connected as Signal, ALERT_n Pin must be bounded to VDD on board. |

| TEN                                          | Input             | Connectivity Test Mode Enable: Required on x16 devices and optional input on x8 with densities equal to or greater than 8Gb. HIGH in this pin will enable Connectivity Test Mode operation along with other pins. It is a CMOS rail to rail signal with AC high and low at 80% and 20% of VDD. Using this signal or not is dependent on System. This pinmay be DRAM internally pulled low through a weak pull-down resistor to VSS.                                                                                                                                         |

| Symbol                                                    | Type   | Function                                                   |

|-----------------------------------------------------------|--------|------------------------------------------------------------|

| NC                                                        |        | No Connect: No internal electrical connection is present.  |

| V <sub>DDQ</sub> Supply DQ Power Supply: 1.2 V +/- 0.06 V |        | DQ Power Supply: 1.2 V +/- 0.06 V                          |

| $V_{SSQ}$                                                 | Supply | DQ Ground                                                  |

| $V_{DD}$                                                  | Supply | Power Supply: 1.2 V +/- 0.06 V                             |

| V <sub>SS</sub>                                           | Supply | Ground                                                     |

| $V_{pp}$                                                  | Supply | DRAM Activation Power Supply: 2.5V (2.375V min , 2.75 max) |

#### 4. ROW AND COLUMN ADDRESS TABLE

| Configu      | uration      | 512Mb x 8 |  |  |

|--------------|--------------|-----------|--|--|

|              | # of Bank    | 4         |  |  |

|              | Groups       | 4         |  |  |

| Bank Address | BG Address   | BG0~BG1   |  |  |

|              | Bank Address | BA0~BA1   |  |  |

|              | in a BG      | BAU-BAI   |  |  |

| Row Address  |              | A0~A14    |  |  |

| Column /     | Address      | A0~ A9    |  |  |

| Page         | size         | 1 KB      |  |  |

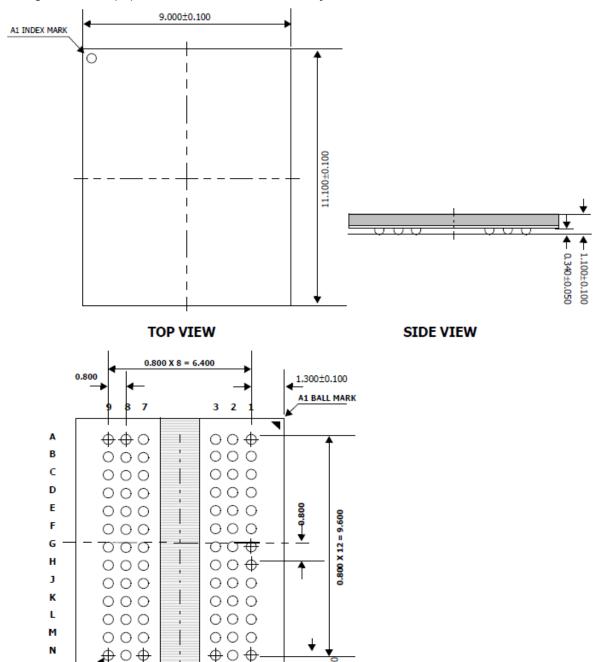

## 5. Package Dimensions

Package Dimension(x8): 78Ball Fine Pitch Ball Grid Array Outline

78 x \(\phi 0.450 \pm 0.050 \)

1.600 1.600

**BOTTOM VIEW**

Zetta

# 6. Revision History

|                                   | Doc. No. | Date    | Comments                  |

|-----------------------------------|----------|---------|---------------------------|

| 01/2016 Initial document release. |          | 01/2016 | Initial document release. |